#### UNIVERSITY OF CALIFORNIA AT BERKELEY

BERKELEY • DAVIS • IR VINE • LOS ANGELES • RIVERSIDE • SAN DIEGO • SAN FRANCISCO

SANTA BARBARA • SANTA CRUZ

CS 150 - Spring 1992 Prof. A. R. Newton

Department of Electrical Engineering and Computer Sciences

## **Quiz 2 Solutions**

(1) (a) The binary string "10110101" is the 8-bit two's complement representation of a fixed point number. What is its decimal value?

- (b) Design a circuit to compute the **two's complement** of a **3-bit binary number**. The inputs are b<sub>0</sub>, b<sub>1</sub> and b<sub>2</sub>, where b<sub>2</sub> is the most significant digit and the outputs are c<sub>0</sub>, c<sub>1</sub> and c<sub>2</sub> where c<sub>2</sub> is the most significant digit.

- (i) Show a **truth table** for the circuit.

- (ii) Draw Karnaugh maps for each output and use them to simplify the functions.

- (iii) Draw a schematic diagram using the minimum number of NAND gates and inverters only.

#### 1(b) (15pts)

(i) Truth table:

| b <sub>2</sub> | <b>b</b> <sub>1</sub> | $\mathbf{b_0}$ | c <sub>2</sub> | c <sub>1</sub> | c <sub>0</sub> |

|----------------|-----------------------|----------------|----------------|----------------|----------------|

| 0              | 0                     | 0              | 0              | 0              | 0              |

| 0              | 0                     | 1              | 1              | 1              | 1              |

| 0              | 1                     | 0              | 1              | 1              | 0              |

| 0              | 1                     | 1              | 1              | 0              | 1              |

| 1              | 0                     | 0              | 1              | 0              | 0              |

| 1              | 0                     | 1              | 0              | 1              | 1              |

| 1              | 1                     | 0              | 0              | 1              | 0              |

| 1              | 1                     | 1              | 0              | 0              | 1              |

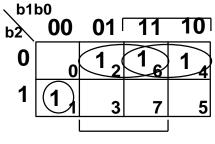

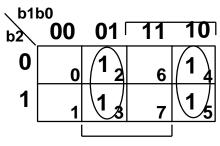

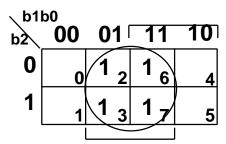

(ii) Karnaugh Maps:

$$c2 = b2'b0 + b2'b1 + b2'b1b0'$$

$$c1 = b1'b0 + b1b0'$$

=  $b1 \text{ xor } b0$

$$c0 = b0$$

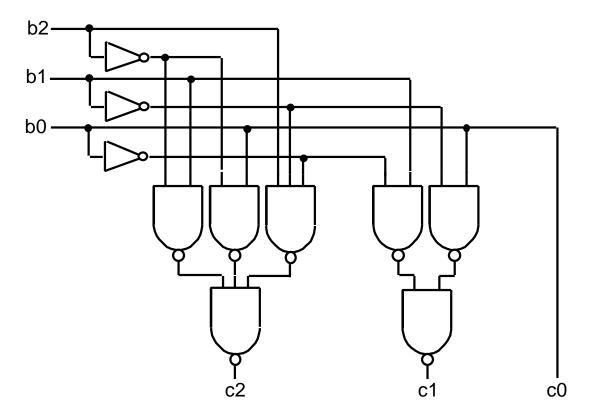

#### (iii) Schematic diagram:

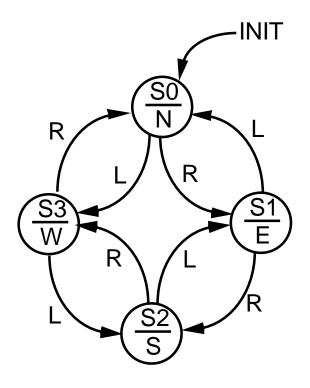

- (2) You are to design a "Manhattan Compass" which is an automobile accessory which has four display lights labelled North, South, East, and (yes, you guessed it...) West. One of the lights is always lit and indicates which direction the car is facing. There are two sensors on the steering wheel, labelled Right and Left. The wires connected to each of the right and left sensors has the value 1 when the position of the steering wheel is to the right or left of center respectively and a value of 0 otherwise. In addition, there is a button labelled INIT which, when pushed, tells the system that the car is stationary, the steering wheel is centered (neither right nor left) and the car is facing north. In Manhattan, all turns are exactly 90 degrees once initiated (U turns are not permitted). Your design is to be a clocked synchronous circuit of the Moore form. Assume the clock signal CLK is derived from the left and right signals.

- (a) Provide a **state transition graph for a Moore implementation** of the compass. **Use the minimum number of states**.

- (b) Provide a **state table** for the compass.

- (c) Derive the **flip-flop input equations** and **compass output equations** for an implementation which uses **clocked D flip-flops**. Assume the INIT signal is used to reset the flip flops. Draw a **schematic diagram** for your circuit, including the D flip-flops and a minimum number of logic gates (no multiplexors!). **Show all Karnaugh maps used**.

#### 2(a) (4pts) State Transition Graph:

# 2(b) (2pts) State Table:

|   | Inp | out | P. | S. | N. | .S. | Output |   |   |   |

|---|-----|-----|----|----|----|-----|--------|---|---|---|

|   | L   | R   | Q1 | Q0 | D1 | D0  | N      | Е | S | W |

| N | 0   | 1   | 0  | 0  | 0  | 1   | 0      | 1 | 0 | 0 |

| N | 1   | 0   | 0  | 0  | 1  | 1   | 0      | 0 | 0 | 1 |

| Е | 0   | 1   | 0  | 1  | 1  | 0   | 0      | 0 | 1 | 0 |

| Е | 1   | 0   | 0  | 1  | 0  | 0   | 1      | 0 | 0 | 0 |

| S | 0   | 1   | 1  | 0  | 1  | 1   | 0      | 0 | 0 | 1 |

| S | 1   | 0   | 1  | 0  | 0  | 1   | 0      | 1 | 0 | 0 |

| W | 0   | 1   | 1  | 1  | 0  | 0   | 1      | 0 | 0 | 0 |

| W | 1   | 0   | 1  | 1  | 1  | 0   | 0      | 0 | 1 | 0 |

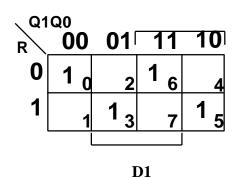

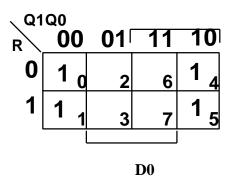

# 2(c) (i) (2pts) Karnaugh Maps:

(ii) (6pts) Flip-flop Input Equations & clock generation:

\_D1 = (Q1 xor Q0 xor R)'\_\_\_\_\_

$_{D0} = Q0'_{}$

$CLK = \underline{L} + R\underline{\phantom{A}}$

(iii) (4pts) Output Equations:

$N = _{Q0'Q1'}$   $E = _{Q1'Q0}$

$S = _{Q1Q0'} W = _{Q1Q0}$

(iv) (7pts) Schematic Diagram:

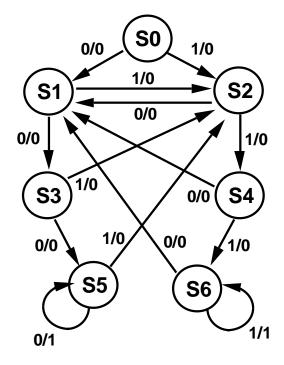

(3) Consider the state table for a Mealy machine shown below:

|       | next           | state | output Z |     |  |

|-------|----------------|-------|----------|-----|--|

|       | x=0            | x=1   | x=0      | x=1 |  |

| $s_0$ | $s_1$          | $s_2$ | 0        | 0   |  |

| $s_1$ | $s_3$          | $s_2$ | 0        | 0   |  |

| $s_2$ | $s_1$          | $s_4$ | 0        | 0   |  |

| $s_3$ | S <sub>5</sub> | $s_2$ | 0        | 0   |  |

| $s_4$ | $s_1$          | $s_6$ | 0        | 0   |  |

| $S_5$ | $S_5$          | $s_2$ | 1        | 0   |  |

| $s_6$ | $s_1$          | $s_6$ | 0        | 1   |  |

- (a) Draw a **state transition graph** for the machine showing all input/output transitions and symbolic states.

- (b) Use the **guidelines presented in class for state assignment** to select an optimal state assignment (for minimum logic). **Show all constraints**, your **final state assignment**, and indicate **which constraints are not satisfied by the assignment**.

- (c) If a **ROM** where used to implement the next-state and output logic for a **D-flip-flop-based** implementation of your machine, how big would it have to be?

### 3(a) (4 pts) State Transition Graph:

#### 3(b) (i) (6 pts) Constraints:

Guideline 1: \_{S0,S1,S3,S5}, {S3,S5}, {S4,S6}, {S0,S2,S4,S6}\_\_\_

Guideline 2: \_{S1,S2}, {S2,S3}, {S1,S4}, {S2,S5}x2, {S1,S6}x2\_

Guideline 3: \_\_{S0,S1,S2,S3,S4,S6}, {S0,S1,S2,S3,S4,S5}\_\_

(ii) (3 pts) Karnaugh Map for Assignment:

| AB | C <sub>00</sub> | 01              | 11              | 10              |

|----|-----------------|-----------------|-----------------|-----------------|

| 0  | SO <b>0</b>     | S2 <sub>2</sub> | S46             | S6 <sub>4</sub> |

| 1  | 1               | S5 <sub>3</sub> | S3 <sub>7</sub> | S1 <sub>5</sub> |

|    |                 |                 |                 |                 |

| A | C <sub>00</sub> | <b>01</b> <sup>[</sup> | 11              | 10              |

|---|-----------------|------------------------|-----------------|-----------------|

| 0 | SO <sub>0</sub> | S1 <sub>2</sub>        | က္တ             | S5 <sub>4</sub> |

| 1 | 1               | S6 <sub>3</sub>        | S4 <sub>7</sub> | S2 <sub>5</sub> |

|   |                 |                        |                 |                 |

(iii) (3 pts) Final State Assignment:

$$S_0 = _000_$$

$$S_1 = _110_$$

$S_2 = _001_$

or

$$S_3 = _111_$$

$$S_4 = 011$$

$$S_4 = _011_$$

$S_5 = _101_$   $S_6 = _010_$

$$S_6 = _010_$$

(iv) (3 pts) Constraints not satisfied:

\_\_\_all output constraints\_\_\_\_\_

**3(c) (6pts) ROM size:**

Number of address lines: \_\_4\_\_

Number of data bits at each address: \_\_3 or 4\_\_

Total number of ROM bits:  $(2^4)4 = 64$  or  $(2^4)3 = 48$