#### Microelectronic Devices and Circuits- EECS105 Final Exam

Tuesday, December 17, 2002

Costas J. Spanos University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Sciences

| Your Name:                                | OFFICI.                                     | AL 30                           | LUTIONS                                  |                                    |

|-------------------------------------------|---------------------------------------------|---------------------------------|------------------------------------------|------------------------------------|

|                                           | (last)                                      |                                 | (first)                                  |                                    |

| Your Signature                            | :                                           |                                 | . · ·                                    |                                    |

| 1. Print and sign yo                      | ur name on this pag                         | ge before ye                    | ou start.                                |                                    |

|                                           | three, 8.5"x11" hai                         |                                 |                                          |                                    |

| 3. Do everything on                       | this exam, and ma                           | ke your met                     | hods as clear as p                       | ossible.                           |

| 4. Always show the<br>worth 70% of the cr | expression before y<br>edit. A correct calc | ou do the fi<br>ulation get     | nal calculation. A<br>s tou you the rema | correct expression i<br>ining 30%. |

|                                           | Problem 1                                   |                                 | /40                                      |                                    |

|                                           | Problem 2                                   |                                 | / 25                                     |                                    |

|                                           | Problem 3                                   |                                 | / 35                                     |                                    |

|                                           | TOTAL                                       |                                 | /100                                     |                                    |

| MOS Device Data <sup>1</sup>              | (you may not have                           | to use all o                    | f these)                                 |                                    |

| $\mu_n C_{ox} = 50 \mu A/V^2, \mu$        | $_{p}C_{ox} = 25\mu A/V^2$ , V              | $T_n = -V_{Tp} =$               | l V, Lmin = 2μm. `                       | $V_{\rm BS} = 0.$                  |

|                                           | en $L = 1 \mu m$ , and it                   |                                 |                                          | 'L                                 |

| $C_{ox} = 2.3 fF/\mu m^2, C_j$            | $_{n} = 0.1 fF/\mu m^{2}, C_{jp} =$         | : 0.3fF/μm <sup>2</sup>         | $C_{jswn} = 0.5 fF/\mu m$                |                                    |

| $C_{jswp} = 0.35 fF/\mu m$                | $C_{ovn} = 0.5 fF/\mu m, C_o$               | $_{\rm typ} = 0.5 {\rm fF}/\mu$ | ım                                       |                                    |

| BJT Device Data (y                        | ou may not have to                          | use all of t                    | hese)                                    |                                    |

| $\beta_f = 100, I_S = 10^{-17} A,$        | 020111                                      | =25V, τ <sub>F</sub> =50        | ps, C <sub>je</sub> =15fF@V <sub>B</sub> | E=0.7V,                            |

| $C\mu=10 fF@V_{BC}=-2$ .                  | 0V                                          |                                 |                                          |                                    |

1 Except as indicated on the particular problem...

2 of 10

# Problem 1 of 3: Answer each question briefly and clearly. (40 points)

1.1 Why circuit nodes with very high impedance matter in terms of frequency response?

becouse they contribute a large RC term.

1.2 When we say that an amplifier stage is "broadband", what do we mean? (4pts)

It is only limited by the It of the device (no Miller effect)

1.3 Place check marks where appropriate (4pts)

| Amp Type | Check if Broadband | Check if high Rin | Check if high Rou |

|----------|--------------------|-------------------|-------------------|

| CS       |                    | ٧                 | V                 |

| CD       | - V                | v                 |                   |

| CG       | V                  |                   | <b>V</b>          |

| CE       |                    |                   | <b>V</b>          |

| CC       | V                  | V                 |                   |

| CB       |                    |                   | V                 |

1.4 Choose the most appropriate answer (3pts)

The Open-Circuit Time Constant method can only work properly if:

... there is one dominant pole and no zeros (actually, 2010) are on if they

... there is an Open Circuit connection happen are frequencies, much Higher

... there is no Miller Capacitance

... the Time is Constant.

than Wo. )

1.5 In this class we talked about the Miller Approximation. Why is it "approximate"? (4pts)

because we squered the current drawn by the Miller up by the output node.

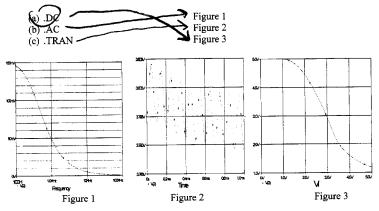

1.6 Match the SPICE control cards (for the types of analysis) to the plots. (3pts)

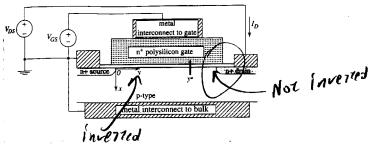

1.7 For the n-channel MOS transistor shown below, please mark the two ends of the channel (near the source and near the drain) and indicate whether or not each must be inverted so that this device is in saturation. (4pts)

1.8 What is the "law of the junction" and when does it apply? (4pts)

| Law of the junction formula:  Pa(Kn) = Pao e                 |  |

|--------------------------------------------------------------|--|

| Mp(-Xp) = Npo e Vu / Vz h  The basic assumption behind it is |  |

| low-level injection.                                         |  |

1.9 What are the two (small signal) capacitive components of a forward biased junction? (4pts)

| Symbol of first capacitance:<br>Verbal Definition:  | depletion | lasfasironse | Cj |

|-----------------------------------------------------|-----------|--------------|----|

| Symbol of second capacitance:<br>Verbal Definition: | Cdiff.    | (ancitaria   |    |

1.10 For each of these circuits, calculate the "no-signal" DC-bias point at the nodes A and B, assuming that every MOS device is biased so that  $V_{GS}$ =1.5V and every BJT is biased so that  $V_{BE}$ =0.7V. After you have done that, circle the circuit that is the "best" in terms of voltage swing at the input  $A^2$  and  $\underline{low}$  frequency response, and explain where the other two fall short. (6pts)

| 5.0 V<br>A    | 5.0 V<br>B<br>I <sub>SUP2</sub> • 2.5 V  |

|---------------|------------------------------------------|

| A - Supi      | 5.0 V<br>B<br>I <sub>SUP2</sub><br>2.5 V |

| 5 <u>.0</u> V | 5. <u>0</u> V                            |

|                         | Best | Explain Performance Limitation      |

|-------------------------|------|-------------------------------------|

| V <sub>A</sub> = 4      |      | Vovi, may = 3.5V                    |

| $V_B = \frac{3}{3}$ . 2 |      | Vint, min = 0.30                    |

| =                       |      | VA=4-(WELLENTETEN)                  |

|                         |      | Coupling (AP o problem              |

| VA = 4.7                |      | Vout, wax = 78 V                    |

| $V_B = 3. Z$            |      | Vont : 100 = 0.5 V                  |

|                         |      | Va=4.7 (NOT LEATENS                 |

| VA = 1.7                |      | Vous , max = 3.8 V                  |

| $V_B = 3.2$             | /    | Vont. ~ m = 0.8 V                   |

|                         |      | VA = 1.7 (9000!) (almost centered). |

## Problem 2 of 3: Answer each question briefly and clearly. (25 points)

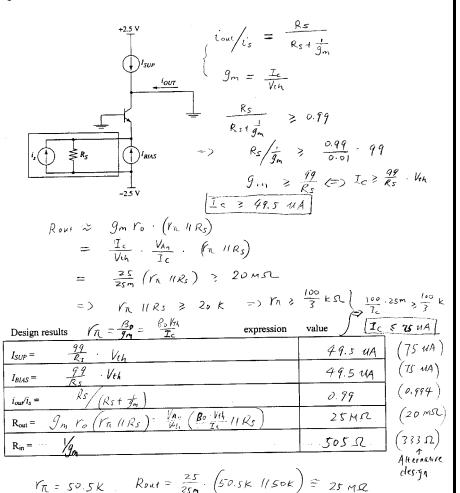

2.1 Design a Common Base "current buffer" amplifier stage so that it meets the following constraints: Total  $R_{out} > 20M\Omega$  if  $R_s = 50k\Omega$ , and an absolute current gain  $i_{out}/i_s$  greater than 0.99, when the stage output is shorted. (Use the simplified formulae that assume that  $g_m r_o >> 1$ ,  $r_n$ ,  $r_o >> 1/g_m$ ,  $r_o$ ,  $r_o c >> R_L$  and that the intrinsic current gain,  $A_i = -1$ .) (13pts)

Note that the input voltage should not be allowed to go over 5V during the operation of these amps. Assume that all the current sources in this question have a minimum voltage drop of 0.5V.

2.2 Write the 2-port model of this amplifier, add the  $C_\pi$  and  $C_\mu$  parasitic capacitances at the proper locations and calculate  $C_\pi$  (assume that  $V_{BC}$ =-2V). Then, assuming that  $R_L$ =0 (shorted) find the pole of this amplifier and draw the magnitude and phase Bode plot of the current gain  $i_{out}/i_x$  (12 pts)

<sup>&</sup>lt;sup>3</sup> Please make sure that you draw the 2-port, and not the small signal model...

#### 8 of 10

## Problem 3 of 3: Answer each question briefly and clearly. (35 points)

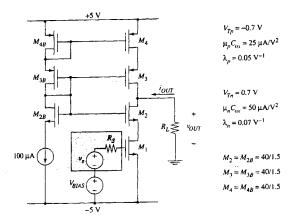

3. Please do a complete analysis of this transconductance amplifier as follows. Make sure that you use the transistor parameters shown below.

3.1 Calculate  $(W/L)_1$  of  $M_1$  such that the small-signal transconductance  $i_{out}/v_s=1 mS$ . Assume  $R_L=0\Omega$  for this part. (7pts)

$$\frac{W}{L} = \frac{9m^2}{2hn(ox Ip}$$

|                         | expression value |     |

|-------------------------|------------------|-----|

| $(W/L)_1 = g_{M_1}$ Ims | : 601            | 150 |

| 2 km Cox Iv             |                  |     |

| 100 <sub>f</sub> A      |                  |     |

3.2 Calculate the value of  $V_{BIAS}$  using the  $(W/L)_I$  calculated in part a so that  $I_{OUT}$  = 0A. (7pts)

lour commut be DA, since the output voltage country to as low as zero (Mr would fall out of saturation!).

in steady-state.

3.3 Calculate the output resistance of this amplifier. (7pts)

Fo = Pup // Edown

Pul = 703+704 + 9m3 703704 = 15M

Polown = 702+701+9m2701702 = 10.6M

expression

value

Rout = (Po) + Po4 + 9m, 20,7001) // (Poz + Po1 + 9m, 20,701) 6.23 MD

3.4 Find the maximum and the minimum value of the output voltage, and state which transistor limits it in each case, when unloaded ( $R_L$ =infinity) (7pts)

|                                 | expression | value |

|---------------------------------|------------|-------|

| vout max = VG3 -VIn             |            | 3.22  |

| limited by: M3, whose yare is   | at 1.571   |       |

| vout min = VGZ -VTN             |            | 182 V |

| limited by: M2, whose sare is a | t 7.52V    |       |

3.5 What is the maximum value of the load resistor  $R_L$  at which the overall transconductance is degraded by 20% from the original value of 1mS? (7pts)

|                      |                                    | expression | value  |

|----------------------|------------------------------------|------------|--------|

| R <sub>L max</sub> = | $lour\left(\frac{1}{0.8}-1\right)$ |            | 1.56MQ |