# EE105, Spring 1997 Midterm #2 Professor R. T. Howe

(NOTE: Greek letters are sometimes written in Roman alphabet in all caps. Subscripts are written A\_1, etc. Micro is sometimes represented by a 'u'.)

Default bipolar transistor parameters:

Default MOS transistor parameters: note that LAMBDA depends on L!

NMOS:

$$MU_nC_ox = 50 \text{ uAV}^2$$

,  $LAMBDA_n = [0.1/L]V^1(L \text{ in um}) V_n = 1V$ . PMOS:  $MU_pC_ox = 25 \text{ uAV}^2$ ,  $LAMBDA_p = [0.1/L]V^1(L \text{ in um}) V_n = -1V$ .

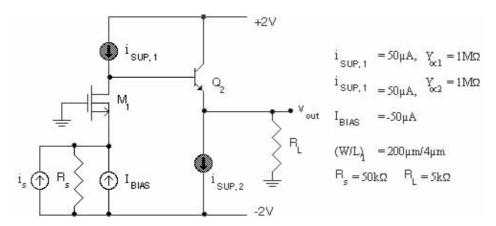

### Problem #1

BiCMOS Transresistance Amplifier [22 points]

- (a) [4 pts.] Draw the two-port small-signal model for this two-stage amplifier, with the small-signal source (and  $R_S$ ) and the load resistor  $R_L$  attached. Your model should show the cascaded models for each stage; there is no need to substitute the expressions for the input and output resistances and gain elements for each stage.

- (b) [4 pts.] Find the numerical value of the input resistance of this amplifier, R\_in.

- (c) [4 pts.] Find the numerical value of the output resistance of this amplifier, R\_out. Your answer need only be correct to within plus or minus 5% for full credit.

- (d) [6 pts.] Find the numerical value of the transresistance  $R_m$ . Note that  $R_s = infinity$  and  $R_L = infinity$  for calculating this two-port parameter. Your answer need only be correct to within plus or minus 5% for full credit.

- (e) [4 pts.] If the current supplies I\_BIAS, i\_SUP,1, and i\_SUP,2 all need a minimum voltage of 0.5 V across

them in order to function, what are the maximum and minimum values of v\_OUT? (In other words, find the output swing of the transresistance amplifier.)

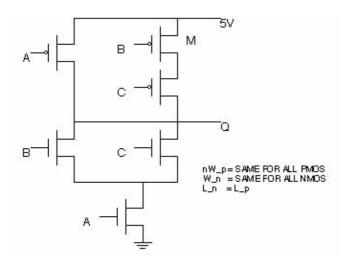

## Problem #2

Static CMOS Logic Gate [18 points]

- (a) [5 pts.] What is the logic operation performed by the above circuit? In other words, what is the logical expression for Q in terms of the three inputs, A, B, and C? Note: you can use a truth table to answer this question.

- (b) [4 pts.] We would like to have the worst case low-to-high and high-to-low propagation delays to be equal. Find the required relationship between the width-to-length ratio (W/L)\_n of the NMOS transistor and the width-to-length ratio (W/L)\_p of the PMOS transistors.

- (c) [5 pts.] This logic gate has no load capacitance or wire capacitance (it does have parasitic drain-to-bulk capacitances, however.) Find the channel length transistors  $L_p = L_n$  so that the worst case low-to-high propagation delay  $t_p = 10^-11s = 100$ ps.

Given:  $MU_p = 100 \text{ cm}^2/\text{Vs}$ ,  $C_ox = 2.5 \text{ fF/um}^2$ , and the drain-to-bulk capacitance of each transistor is  $C_ox = 100 \text{ cm}^2/\text{Vs}$ ,  $C_ox = 100 \text{ cm}^2/\text{Vs}$ ,  $C_ox = 100 \text{ cm}^2/\text{Vs}$ , and the drain-to-bulk capacitance of each transistor is  $C_ox = 100 \text{ cm}^2/\text{Vs}$ .

If you couldn't solve part (b), you can assume that  $(W/L)_p = 2.5(W/L)_n$  for this part (not the correct answer to (b), of course.)

(d) [4 pts.] Find the ratio of the **best case** propagation delays.

### t\_PHL/t\_PLH

If you couldn't solve (b), you can assume that  $(W/L)_p = 2.5 (W/L)_n$  for this part (not the correct answer to (b), of course.)

Problem #1

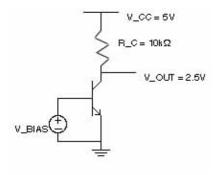

### Problem #3

Bipolar Transistor Physics [10 points]

Note: the default npn transistor parameters do not apply to this problem!

#### Given:

N\_dE = 10^18cm^-3, N\_aB = 5 X 10^16cm^-3, N\_dC = 4 X 10^15cm^-3.

The base and emitter widths are  $W_B = W_E = 0.25$  um. The area of the emitter-base junction is  $A_E = 1000$  um<sup>2</sup> and the area of the base-collector junction is  $A_C = 3000$  um<sup>2</sup>. The electron diffusion coefficient in the base is  $D_nB = 10$ cm<sup>2</sup>/s and the hole diffusion coefficient in the emitter is  $D_pE = 5$ cm<sup>2</sup>/s. The charge on an electron is  $q = 1.6 \times 10^{-19}$ C.

- (a) [5 pts.] For the bias condition where  $V_{OUT} = 2.5V$ , sketch the minority carrier concentration in the base on the graph below. Label the numerical value of  $n_{DB}$  (x = 0).

- (b) [5 pts.] Find the numerical value for the bias voltage  $V_BIAS$  for which the bipolar transistor just enters saturation ( $V_OUT = 0.2V$ ).

### **Solutions!**

Posted by HKN (Electrical Engineering and Computer Science Honor Society)

University of California at Berkeley

If you have any questions about these online exams

please contact <u>examfile@hkn.eecs.berkeley.edu.</u>

Problem #3