# UNIVERSITY OF CALIFORNIA, BERKELEY

# College of Engineering Department of Electrical Engineering and Computer Sciences

## FINAL EXAMINATION

EE 130/230M: IC Devices, Fall 2012 Time allotted: 75 minutes

| NAME:        |                                                                          |                  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------|------------------|--|--|--|--|--|

| STUDENT ID#: |                                                                          |                  |  |  |  |  |  |

| INST         | TRUCTIONS:                                                               |                  |  |  |  |  |  |

| 1.           | Unless otherwise stated, assum a. temperature is 300 K b. material is Si | e                |  |  |  |  |  |

| 3.           | Specially, while using char                                              | x) your answers. |  |  |  |  |  |

|              | SCORE:1                                                                  | /20              |  |  |  |  |  |

|              | 2                                                                        | / 20             |  |  |  |  |  |

|              | 3                                                                        | /20              |  |  |  |  |  |

|              | Total                                                                    | 160              |  |  |  |  |  |

## PHYSICAL CONSTANTS

| <u>Description</u>   | Symbol             | <u>Value</u>            | PROPERTIES OF SILICON AT 300K |                             |                             |  |

|----------------------|--------------------|-------------------------|-------------------------------|-----------------------------|-----------------------------|--|

| Electronic charge    | q                  | 1.6×10 <sup>-19</sup> C | <u>Description</u>            | <u>Symbol</u>               | <u>Value</u>                |  |

| Boltzmann's constant | k                  | $8.62 \times 10^{-5}$   | Band gap energy               | $E_{\mathbf{G}}$            | 1.12 eV                     |  |

|                      |                    | eV/K                    | Intrinsic carrier             | $n_{\mathrm{i}}$            | $10^{10}  \mathrm{cm}^{-3}$ |  |

| Thermal voltage at   | $V_{\mathrm{T}} =$ | 0.026 V                 | concentration                 |                             |                             |  |

| 300K                 | kT/q               |                         | Dielectric permittivity       | $\mathcal{E}_{\mathrm{Si}}$ | $1.0 \times 10^{-12}$       |  |

|                      | _                  |                         |                               |                             | F/cm                        |  |

## **USEFUL NUMBERS**

$V_T \ln(10) = 0.060 \text{ V}$  at T=300K exp $(0.6/0.26)\sim 10^{10}$

Depletion region Width:

$$W = \sqrt{\frac{2\varepsilon}{q} \left( \frac{1}{N_a} + \frac{1}{N_d} \right) \left( V_{bi} - V_{Applied} \right)}$$

Law of the Junction:  $np = n_i^2 \left(e^{qV_D/kT}\right)$

$N_c = 2.8 \times 10^{19} / \text{cm}^3$

$N_V = 1.04 \times 10^{19} / \text{cm}^3$

### Prob 1. [20 pts]

- (a) [4 pts] Answer the following

- (i) [2 pts] What are the main physical mechanisms for drift and diffusion?

Drift -> acceleration due to electric field Diffusion -> Mandom thermal motion

(ii) [2 pts] Between two diodes, one more heavily doped than the other, which one will have a smaller reverse breakdown voltage? Why?

The heavily doped one. Due to high doping, built in E-field will be high and large band overlap will occur at event relatively small reverse bias. This will lead to tanneling and then breakdown.

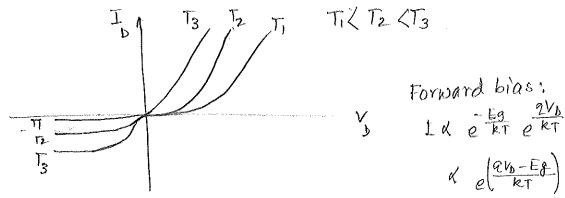

(b) [5 pts] Drawing an I-V plot show how *increasing temperature from 300°K* will change the current voltage characteristic of a diode. You should show three different I-Vs each for a different temperature. In the plots carefully show if there is any difference in the extent of change in current for forward and reverse bias. Briefly justify reasons for any such difference.

Reverse bias:

Ide Eg/kr

Diode range of operation for low level

At same [Vo] increase in forward bias current is less than reverse bias current.

(c) [5 pts] Consider a pn junction diode doped such that  $N_A=10^{17}/\text{cm}^3$  and  $N_D=10^{15}/\text{cm}^3$ . A bias is applied such that at the edge of the depletion region on the p-side the number of electrons is found to be  $10^8/\text{cm}^3$ . Is the diode forward or reverse biased? Justify your answer. Also find out the amplitude of the bias voltage applied across the diode.

across the diode.

$$n_p = 108$$

;  $m_b = \frac{1020}{1017} = 10^8$ .  $n_p > n_p \rightarrow forward$  biased.

$$\delta n_p = \frac{n_i^2}{N_A} / \frac{2V_D}{RT}$$

$$\Rightarrow 10^8 = \frac{10^{20}}{10^{17}} = \frac{\sqrt{60026}}{0.026}$$

$$\frac{10^{5}}{2} = \frac{10^{5}}{2} = \frac{10$$

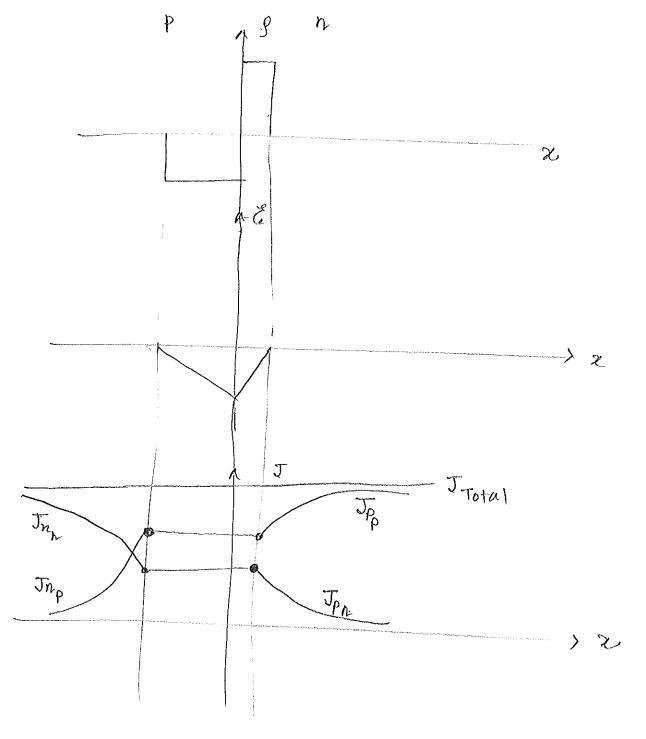

(d)[6 pts] Consider a pn junction diode is biased such that the n-side has a higher doping than the p-side. Qualitatively draw:

- (i) The charge density profile

- (ii) The electric field profile

- (iii) The current density profile in the forward bias

### Prob 2 [20 pts]

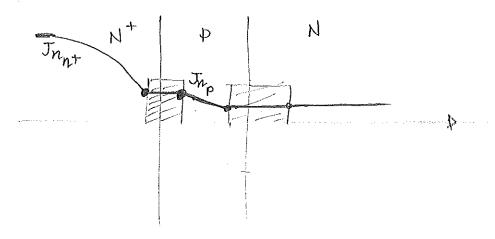

(a) [5 pts] Consider a short base N<sup>+</sup>PN junction. Draw the current density profile due to electrons in the various regions of the junction in the forward active mode. Comment on how it will change if the base width is increased. In both cases, assume that emitter and collector regions are much longer than diffusion lengths.

The amplitude of collector current density will decrease with increasing base width because more and more carriers will be lost in the base due to recombination

(b) [9 pts] Two pnp BJTs are designed such that:

T1:  $N_{E1} > N_{B1} > N_{C1}$

T2: N<sub>c2</sub>>N<sub>B2</sub>>N<sub>E2</sub>

In both cases, the base doping is the same  $N_{B1}=N_{B2}$ . Also,  $N_{E1}=N_{C2}$ .

- (a) Which transistor is expected to have greater emitter efficiency? Explain.

- (b) Which transistor will exhibit greater sensitivity to base width modulation under active mode biasing? Explain.

- (c) Which transistor will breakdown at smaller voltages? Explain.

- (a) T1: more carriers will be injected from comitter than from base

- (b) T2: Breance base will get a larger depletion region

- ( to: B-C Junction has night doping.

(c)[6 pts]

(i) [3 pts] How will changing the base width affect the speed of a bipolar transistor?

increasing base width will increase the streage time.

(ii) [3 pts]  $\beta$ =I<sub>C</sub>/I<sub>B</sub> falls down at very high and low levels of collector current. What are the reasons for that?

nigh currents -> hish I wel inviction low currents -> junction leakage.

## Prob 3[20 pts]

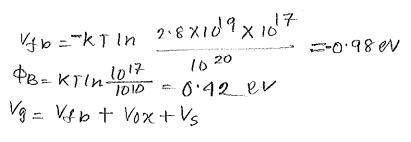

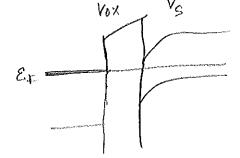

(a) [8 pts] Consider a MOS capacitor with N+ polysilicon gate that has a doping of  $N_D=2.8 \times 10^{19}/cm^3$ . Assume the applied gate voltage is 0.5 V and a body doping of  $N_A=10^{17}/cm^3$ . Find out the voltage drop across the gate oxide if it is known that, at this gate voltage, the depletion region width in the body is 110 nm. What will be the voltage drop across oxide if the gate voltage is increased to 0.7 V?

$$W = 110 \times 10^{7} = \sqrt{\frac{26}{9NA}} V_{S}$$

$$\frac{V_{0x} = V_{g} - V_{fb} - V_{s} = +0.5 - (-0.98) -0.923}{V_{0x} = 0.5561 \text{ V}}$$

We note: Vs) 2¢B; thus the Mosfet is in inversion. Therefore any increase in gate voltage drops across oxide.

Hence When G=0.7 V

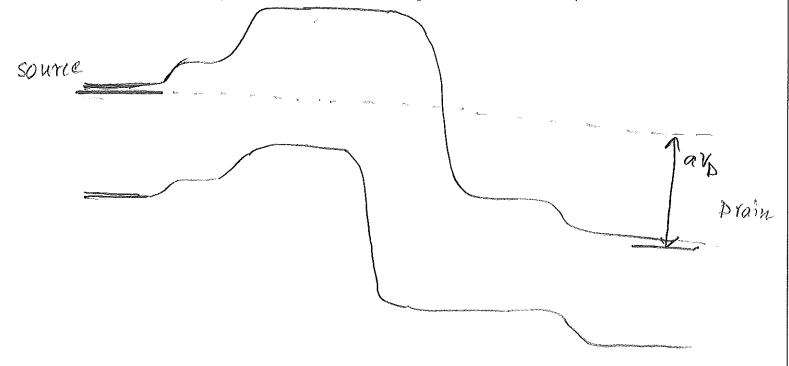

(b) [6 pts] Consider a N+NPNN+ Junction made on a p-type substrate. The N+ regions are connected to metal as source and drain. This structure is topped with a thin  $SiO_2$  and a metal gate. Draw the energy band diagram at the interface between semiconductor and the  $SiO_2$  going from source to drain at the OFF condition. How do you think the inclusion of extra N regions will affect the MOSFET performance?

Extra N+ reduces source resistance.

(c) [6 pts]

(i) [3 pts] Briefly explain DIBL.

lowering of the potential barrier not the source by drain voltage in very small mosfet is caned DIBL. Due to close proximity of drain terminal, drain voltage modulates the channel potential which in a long channel FET is only controlled by gate.

(ii) [3 pts] Si has bandgap of 1.1 eV while InAs has a bandgap of ~0.3 eV . For an ultra scaled transistor, which material will give the most leakage current? Why? Assume that the current due to direct tunneling through gate insulator is the same for both.

InAS -> increased BTBT due to small gap.

-> increased n;2 -> increased reverse saturation

current