# UNIVERSITY OF CALIFORNIA, BERKELEY College of Engineering Department of Electrical Engineering and Computer Sciences

#### **FINAL EXAMINATION 2**

EE 130/230A: Spring 2015 Time allotted: 90 minutes

| NAME  | E:                                                                                                                                                                                                         | Solution                                                                               |                                                                                   |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| STUD! | ENT ID#:                                                                                                                                                                                                   |                                                                                        |                                                                                   |  |  |  |

| INSTR | RUCTIONS:                                                                                                                                                                                                  |                                                                                        |                                                                                   |  |  |  |

| 1. U  | Unless otherwise stated, assume<br>a. temperature is 300 K<br>b. material is Si                                                                                                                            | <b>;</b>                                                                               |                                                                                   |  |  |  |

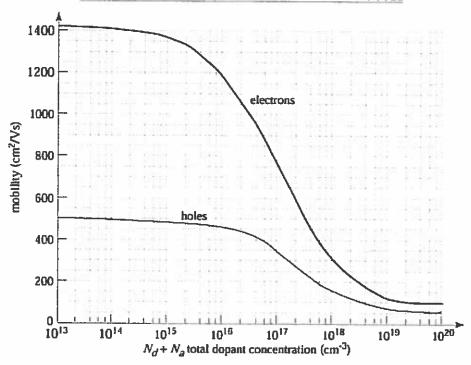

| • (   | SHOW YOUR WORK. (Make  o Specially, while using chart have got your numbers. For write down what doping de  o Clearly write down any ass  Clearly mark (underline or box)  Specify the units on answers wh | t, make sure that<br>example, if reansity that corresumption that you<br>your answers. | t you indicate how you<br>ding off mobility, clearly<br>ponds to.<br>u have made. |  |  |  |

|       | SCORE: 1                                                                                                                                                                                                   | /20                                                                                    |                                                                                   |  |  |  |

|       | 2                                                                                                                                                                                                          | / 20                                                                                   | \$1                                                                               |  |  |  |

|       | 3                                                                                                                                                                                                          | /20                                                                                    |                                                                                   |  |  |  |

|       | Total                                                                                                                                                                                                      | / 60                                                                                   |                                                                                   |  |  |  |

#### PHYSICAL CONSTANTS

| Description          | Symbol        | Value                   | PROPERTIES OF           | SILICON.                    | AT 300K                       |

|----------------------|---------------|-------------------------|-------------------------|-----------------------------|-------------------------------|

| Electronic charge    | q             | 1.6×10 <sup>-19</sup> C | Description             | Symbol                      | Value                         |

| Boltzmann's constant | . k           | 8.62×10 <sup>-5</sup>   | Band gap energy         | $E_{\mathbf{G}}$            | 1,12 eV                       |

|                      |               | eV/K                    | Intrinsic carrier       | $n_i$                       | $10^{10} \text{ cm}^{-3}$     |

| Thermal voltage at   | $V_{\rm T} =$ | 0.026 V                 | concentration           |                             |                               |

| 300K                 | kT/q          |                         | Dielectric permittivity | $\varepsilon_{\mathrm{Si}}$ | 1.0×10 <sup>-12</sup><br>F/cm |

#### **USEFUL NUMBERS**

$V_T \ln(10) = 0.060 \text{ V} \text{ at } T=300 \text{K}$

Depletion region Width:

$$W = \sqrt{\frac{2\varepsilon}{q} \left( \frac{1}{N_a} + \frac{1}{N_d} \right) \left( V_{bi} - V_{Applied} \right)}$$

## Current in a PN junction:

$$I = A \left( q \frac{D_p}{L_p} p_{n0} + q \frac{D_n}{L_n} n_{p0} \right) (e^{qV_D/kT} - 1)$$

#### Electron and Hole Mobilities in Silicon at 300K

Table1: Barrier Heights of Different Metals to Si

| Metal                     | Mg  | Ti   | Cr   | Ni   | W    | Mo   | Pd   | Au  | Pt  |

|---------------------------|-----|------|------|------|------|------|------|-----|-----|

| $\phi_{Bn}\left(V\right)$ | 0.4 | 0.5  | 0.61 | 0.61 | 0.67 | 0.68 | 0.77 | 0.8 | 0.9 |

| $\phi_{Bp}\left(V\right)$ |     | 0.61 | 0.5  | 0.51 |      | 0.42 |      | 0.3 |     |

| Work Function $\psi_m(V)$ | 3.7 | 4.3  | 4.5  | 4.7  | 4.6  | 4.6  | 5.1  | 5.1 | 5.7 |

Table 2:Barriet Heights of Different Silicide Alloys to Si

| Silicide       | ErSi <sub>1.7</sub> | HfSi | MoSi <sub>2</sub> | ZrSi <sub>2</sub> | TiSi <sub>2</sub> | CoSi <sub>2</sub> | WSi <sub>2</sub> | NiSi <sub>2</sub> | Pd <sub>2</sub> Si | PtSi |

|----------------|---------------------|------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|--------------------|------|

| $\phi_{Bn}(V)$ | 0.28                | 0.45 | 0.55              | 0.55              | 0.61              | 0.65              | 0.67             | 0.67              | 0.75               | 0.87 |

| $\phi_{Bp}(V)$ |                     | 0.45 | 0.55              | 0.49              | 0.45              | 0.45              | 0.43             | 0.43              | 0.35               | 0.23 |

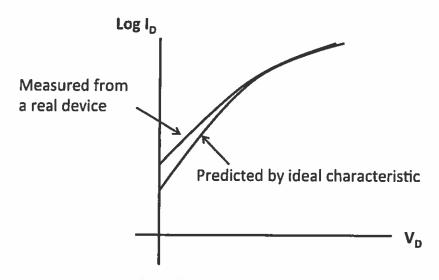

**Problem 1.a** [10 pts] Consider a Si-diode for which I-V characteristic is shown in the following. The measurement is done at room temperature. A discrepancy from the ideal characteristic is seen such that an increased OFF current is observed.

I. [4 pts] What is the likely reason behind the discrepancy between the ideal and measured characteristic? Clearly explain.

The most likely reason is

junction leakage that happens

due to defects which introduce

e- Ev

states in the bandgap. Electrons

can go to the Ec from Er through defect states as shown in the figure - These additional electrons lead to increased current at the OFF state.

II. [3 pts] Will the discrepancy change at elevated temperature? If yes, will it go up or down? Why?

The discrepancy will go up at elevated temp as electrons will have more thermal energy to jump to Ee from Eu

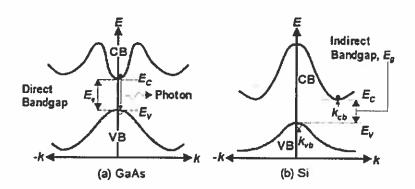

III. [3 pts] Based on the following bandstructure for Si and GaAs, which material will give higher OFF current? Why?

GOAS -> because it is a direct bandgap material, so electrons do not need to change be to go to Ec from Ev.

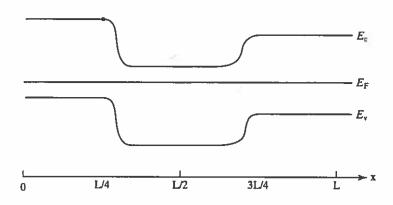

#### Prob 1b. [10 pts]

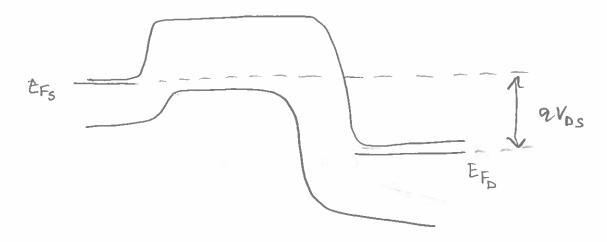

A silicon sample is characterized by the energy band diagram in the following figure:

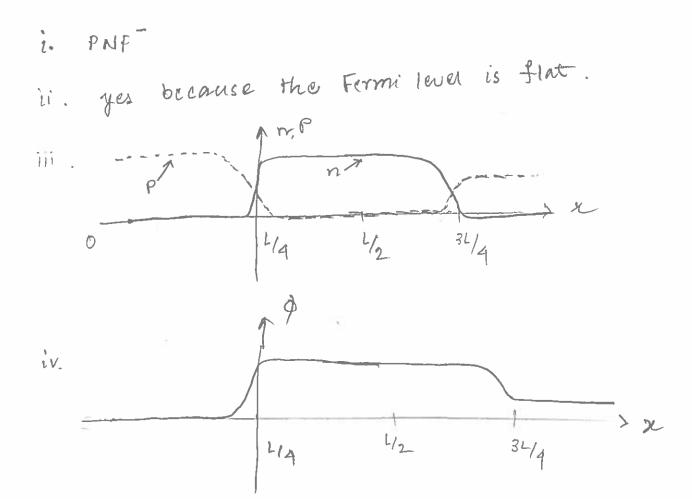

- i. [2.5 pts] What kind of transistor is it?

- ii. [2.5 pts] Does the equilibrium condition prevail? How do you know?

- iii. [2.5 pts] Roughly sketch n and p versus x.

- iv. [2.5 pts] Sketch the electrostatic potential as a function of x.

#### Prob 2 [20 pts]

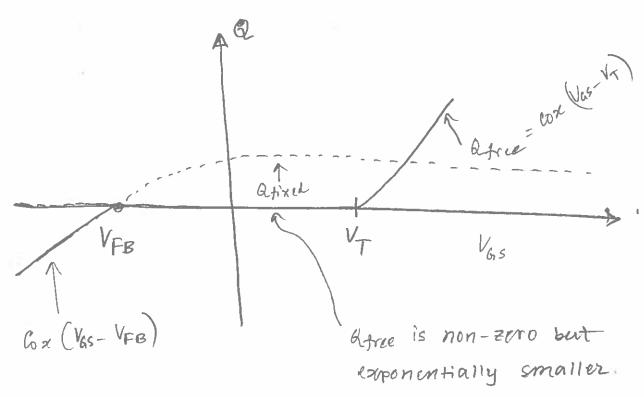

(a) [8 pts] Qualitatively plot the free carrier density as a function of gate voltage in a MOS-capacitor with p-type body. On the same plot show the fixed carrier density as a function of gate voltage. Your plot should clearly show the flatband and threshold voltage points. Assume that the MOS capacitor has highly n<sup>+</sup> doped source /drain regions which are both grounded along with the body for this problem and the only voltage being applied is on the gate.

(b) [4 pts] If it is known that the depletion region width at  $Vgs=V_T$  is 500 nm and the body factor m is 1.3, what is the minimum capacitance? [ $V_T$  is the threshold voltage of the MOSFET]

Minimum capacitance occurs at Vas = 4 where the capacitive network of the depletion region is still valid of the depletion region in the depletion region is still valid of the depletion region in the depletion region is still valid of the depletion region of the depletion region is still valid of the depletion region in the depletion region of the depletion region is still valid of the depletion region of the depletion region is still valid of the depletion region of the d

$$\frac{\mathcal{E}_{Si}}{min} = \frac{\mathcal{E}_{Si}}{mW + max}$$

$$= \frac{11.9 \times 8.854 \times 10^{4}}{1.3 \times 500 \times 10^{7}}$$

$$C = \frac{1.5 \times 10^{8} \text{ F/cm}^{2}}{min}$$

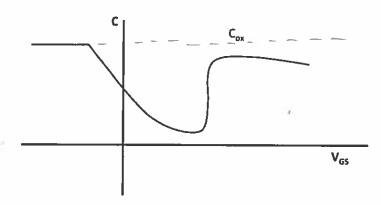

(c) [4 pts] The C-V diagram of a MOS capacitor is shown in the following. Why is the capacitance in the inversion region different from  $Cox=e_{ox}/t_{ox}$  where  $t_{ox}$  is the physical thickness of the insulator. How would a high-k-metal gate (HKMG) technology change it?

The capacitance in the inversion region is différent because

- (i) inversion charge is removed from the si/sioz interface

- (ii) if a poly-gate is used, then there is a boly depletion width

HKMER will make c closer to cox by removing the poly depletion region.

(d) [4 pts] What characteristic in the MOSFET shows the signature of velocity saturation. Can the carrier velocity increase even more after the velocity saturation has happened if the channel length is further reduced? Why /Why not?

Is-Vs characteristic shows linear spacing between traces for different Vg rather than quadratic, in the saturation region [] DSAL & Vas

The velocity can still increase. This is because for a very small channel length corriers my rut get enough time to scatter. Scattering is what determines saturation velocity at high electric fields.

#### Problem 3 [20 pts].

**Problem 3a.** Consider a Si MOSFET with p-type body is being operated at  $V_{GS} < V_T$  ( $V_T$  is the threshold voltage). The drain voltage is set to a high value.

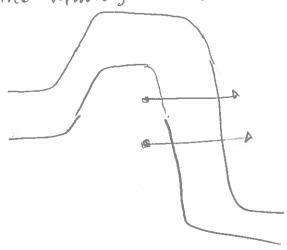

(i) [4 pts] Draw the band diagram at the Si/SiO2 interface looking from source to drain.

#### (ii) [4 pts] Briefly describe how current flows in this regime.

The current flow happens by injecting carriers from the source to the body about to a p-n function diode. Moreover, carriers are swept out at the drawn side by weating a depletion region. This keeps a concentration gradient across the body leading to diffusion of carriers and current flow.

### (iii) [4 pts] If the voltage is continuously reduced, how will the current change?

Initially the current will go down exponentially However at some point carriers will start to tannel from p-body to the drain, leading to an increase in current.

#### Problem 3(b) [8 pts]

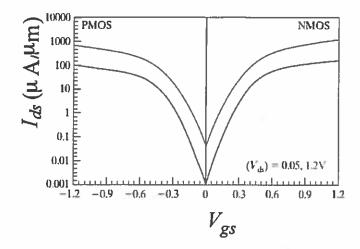

Consider the following characteristic for a Si MOSFET where a change in the id-VG characteristic is seen as a function of drain voltage.

(i) [4 pts] What is this effect called? Briefly explain why this happens.

This effect is called DIBL (Drain induced barrier lower)

or VT roll-off.

As the channel length is reduced so that the drain voltage depletion region reaches the source side p-n simetion, increasing drain voltage converted reduces the barrier neight seen by the source electrons. As a result, current gies up.

(ii) [4 pts] Will this effect be better or worse for a material with larger permittivity than Si (11.9) such as InAs (12.3)?

Wa Jar

so, for the same doping, larger & leads to increase depletion width. This means that for the same channel length, drain side depletion region will reach the source p-n junction at a smaller Vs.

Therefore, the effect will become worse.