# UNIVERSITY OF CALIFORNIA, BERKELEY College of Engineering Department of Electrical Engineering and Computer Sciences

# **MIDTERM EXAMINATION 2**

EE 130/230A: Spring 2016 Time allotted: 60 minutes

| NAMI  | E: SOLUTION                                                                                        |                                                |

|-------|----------------------------------------------------------------------------------------------------|------------------------------------------------|

| STUD  | ENT ID#:                                                                                           |                                                |

| INSTR | RUCTIONS:                                                                                          |                                                |

| 1. 1  | Unless otherwise stated, assum<br>a. temperature is 300 K<br>b. material is Si                     | e                                              |

| • (   | <ul> <li>Specially, while using chathave got your numbers. For write down what doping d</li> </ul> | sumption that you have made.  k) your answers. |

|       | SCORE:1                                                                                            | /20                                            |

|       | 2                                                                                                  | /20                                            |

|       | Total                                                                                              | / 40                                           |

### **PHYSICAL CONSTANTS**

| Description          | Symbol           | <u>Value</u>            | <b>PROPERTIES OF</b>    | SILICON                     | AT 300K                     |

|----------------------|------------------|-------------------------|-------------------------|-----------------------------|-----------------------------|

| Electronic charge    | $\boldsymbol{q}$ | 1.6×10 <sup>-19</sup> C | <u>Description</u>      | Symbol                      | Value                       |

| Boltzmann's constant | k                | 8.62×10 <sup>-5</sup>   | Band gap energy         | $E_{\mathrm{G}}$            | 1.12 eV                     |

|                      |                  | eV/K                    | Intrinsic carrier       | $n_{\rm t}$                 | $10^{10}  \mathrm{cm}^{-3}$ |

| Thermal voltage at   | $V_{T} =$        | 0.026 V                 | concentration           |                             |                             |

| 300K                 | kT/q             |                         | Dielectric permittivity | $\varepsilon_{\mathrm{Si}}$ | $1.0 \times 10^{-12}$       |

|                      |                  |                         |                         |                             | F/cm                        |

### **USEFUL NUMBERS**

$V_{\rm T} \ln(10) = 0.060 \text{ V}$  at T=300 K

# Depletion region Width:

$$W = \sqrt{\frac{2\varepsilon}{q} \left(\frac{1}{N_a} + \frac{1}{N_d}\right) \left(V_{bi} - V_{Applied}\right)}$$

# Current in a PN junction:

$$I = A \left( q \frac{D_p}{L_p} p_{n0} + q \frac{D_n}{L_n} n_{p0} \right) (e^{qV_D/kT} - 1)$$

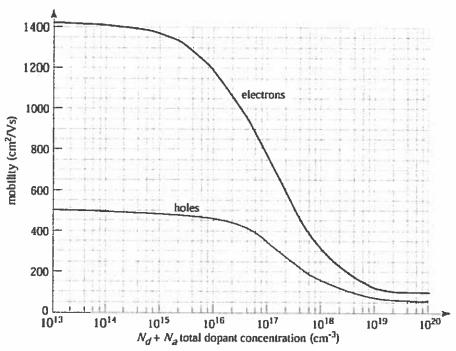

# Electron and Hole Mobilities in Silicon at 300K

Table1: Barrier Heights of Different Metals to Si

| Metal                     | Mg  | Ti   | Cr   | Ni   | W    | Мо   | Pd   | Au  | Pt  |

|---------------------------|-----|------|------|------|------|------|------|-----|-----|

| $\phi_{Bn}\left(V\right)$ | 0.4 | 0.5  | 0.61 | 0.61 | 0.67 | 0.68 | 0.77 | 0.8 | 0.9 |

| $\phi_{Bp}\left(V\right)$ |     | 0.61 | 0.5  | 0.51 |      | 0.42 |      | 0.3 |     |

| Work Function $\psi_m(V)$ | 3.7 | 4.3  | 4.5  | 4.7  | 4.6  | 4.6  | 5.1  | 5.1 | 5.7 |

Table 2:Barriet Heights of Different Silicide Alloys to Si

| Silicide       | ErSi <sub>1.7</sub> | HfSi | MoSi <sub>2</sub> | ZrSi <sub>2</sub> | TiSi <sub>2</sub> | CoSi <sub>2</sub> | WSi <sub>2</sub> | NiSi <sub>2</sub> | Pd <sub>2</sub> Si | PtSi |

|----------------|---------------------|------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|--------------------|------|

| $\phi_{Bn}(V)$ | 0.28                | 0.45 | 0.55              | 0.55              | 0.61              | 0.65              | 0.67             | 0.67              | 0.75               | 0.87 |

| $\phi_{Bp}(V)$ |                     | 0.45 | 0.55              | 0.49              | 0.45              | 0.45              | 0.43             | 0.43              | 0.35               | 0.23 |

## Problem 1 [20 pts]

- (a) [12 pts] Consider a metal-Si junction. It is known that  $\phi_{Bn}$ =0.8 eV. It is also known that the built-in potential is 0.2eV and  $\phi_{ms}$ <0.

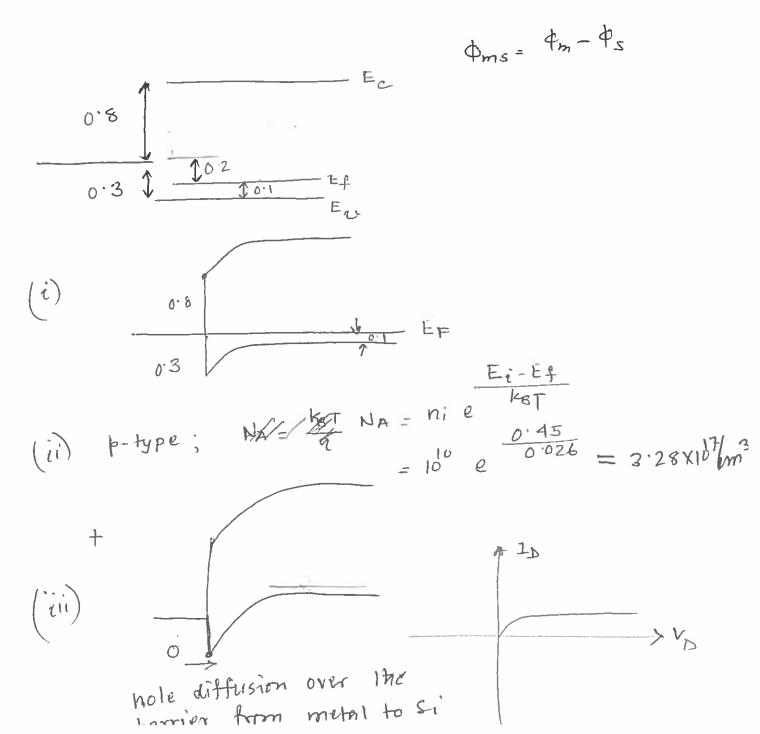

- (i) [4 pts] Draw the energy-band diagram of the junction at equilibrium.

- (ii) [4 pts] Find out the type and doping level of Si.

- (iii) [6 pts] Draw the current voltage characteristics. Explain how current flows by clearly pointing out the mechanism and the directions that electrons and holes are flowing for each polarity of the voltage. For this, positive voltage means that the positive terminal of the battery is connected to the metal and positive current means the current is flowing from the metal to the semiconductor.

(b) [6 pts]

(i) [2 pts] A NPN transistor is biased such that  $V_{BE}$ =0.5 V. Draw the collector current as a function of  $V_{CE}$  for an ideal transistor in the following:

VCB = VCE - VBE

1.0

1.5

VCE (V)

(ii) [4pts] How will the plot in (i) change for a realistic short base transistor? Show by drawing in the same plot in the previous page. What is reason behind this change? What measures are taken to minimize this effect?

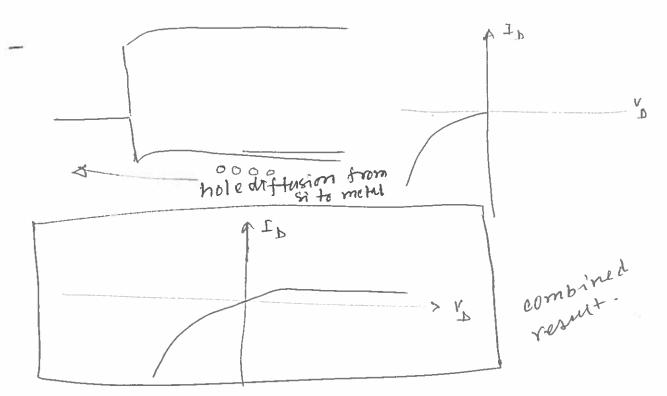

The change happens due to bace width modulation where increasing Vos mireases reverse bias at the collector-base junction, which increases depletion region width, and in turn effective width of the base.

collector is doped more lightly than the base to minimize this effect.

## Problem 2. [20 pts]

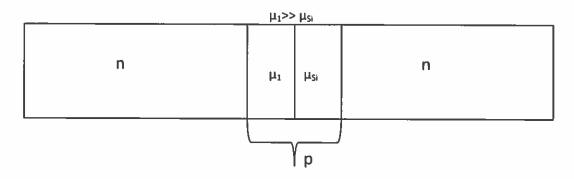

- (a) [10 pts]Consider a NPN bipolar junction transistor as shown below. To increase the collector current, a thin layer of a very high mobility material is inserted into the short base. You can assume that there is no band bending at the interface of these two materials. You can assume that doping level is the same throughout the base.

- (i) [6 pts] Draw the excess minority carrier distribution in the base by clearly showing the two boundaries. Justify your answer.

- (ii) [4 pts] Will this appreciably increase the collector current? Why or why not?

(2) ni2 (e kBT -1) My Msi mi 2 (e RBT -1)  $2D_n \frac{d s n}{d x} = 2D_n \frac{d s n}{d x} |s_i|$ ;  $\frac{D}{R} = \frac{KT}{2L}$ => KBT M, don 1 = KBT Ks; don 1 s1. Just = a Dsi NB [e KBT e LBT] (ii) if base was just si avbe QVBC KBT]  $J = Q D_{si} \frac{hi^2}{NB} \left[ e^{\frac{1}{1}} \frac{Q V_{BC}}{EBT} \right]$

## (b) [6 pt]

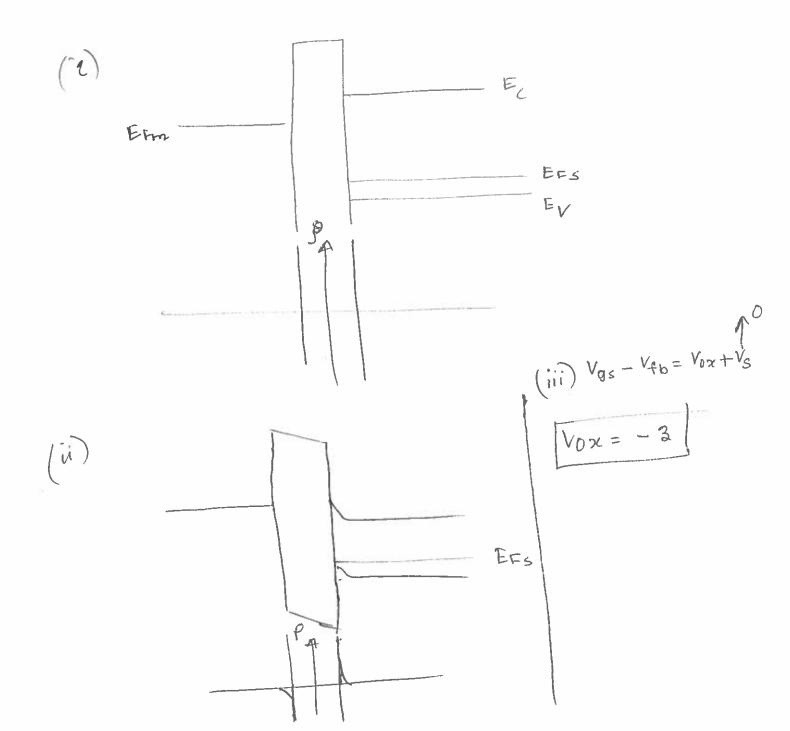

- (i) [2 pt] Draw the energy band diagram of a MOS capacitor at the flatband condition. Assume that the Si has been doped p-type and the gate is made of a metal with  $\phi_{ms}$ <0. Draw the charge density profile at the semiconductor for this bias condition.

- (ii) [2 pt] Repeat problem (i) when  $V_{g_8}$  is made more negative than the flatband voltage.

- (iii) [2 pt] When  $V_{\rm gs}$  is 3V more negative than the Flatband voltage, what is the voltage drop across the oxide?

# (c) Please indicate 'TRUE' or 'FALSE'

| Phenomenon                                                                                                               | TRUE/FALSE |

|--------------------------------------------------------------------------------------------------------------------------|------------|

| In the depletion mode, the semiconductor charge is primarily based on immobile ions                                      | TRUE       |

| For a MOS capacitor with p doped body, one must have Vgs>0 to reach the depletion mode                                   | FALSE      |

| After threshold voltage is reached any further increase in gate voltage almost completely drops across the semiconductor | FALSE      |

| Beyond the threshold voltage free charges increases exponentially as a function of gate voltage                          | FALSE      |