University of California

College of Engineering

Department of Electrical Engineering

and Computer Science

J. M. Rabaey

TuTh9:30-11am ee141@eecs

## EECS 141: FALL 00 —MIDTERM 1

For all problems, you can assume the following transistor parameters (unless otherwise mentioned):

NMOS:

$$V_{Tn} = 0.4$$

,  $k'_n = 115 \mu A/V^2$ ,  $V_{DSAT} = 0.6 V$ ,  $\lambda = 0$ ,  $\gamma = 0.4 V^{1/2}$ ,  $2\Phi_F = -0.6 V$

PMOS:

$$V_{Tp} = -0.4 \text{V}, \, k'_p = -30 \, \mu \text{A/V}^2, \, V_{DSAT} = -1 \, \text{V}, \, \lambda = 0, \, \gamma = -0.4 \, \, \text{V}^{1/2}, \, 2 \Phi_F = 0.6 \, \text{V}$$

| NAME | SOLUTION<br>Last First |  |

|------|------------------------|--|

|------|------------------------|--|

GRAD/UNDERGRAD

Problem 1: 8.5

Problem 2: 10.0

Problem 3: 7.5

Total 26

## PROBLEM 1: Transient Response

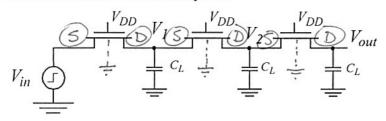

FIG. 1 Digital circuit

Consider the circuit of FIG. 1. All the transistors are originally minimum-size devices. Use the transistor parameters indicated on the first page of the midterm.

$V_{DD} = 2.5 \text{ V}$ .  $C_L = 30 \text{ fF}$ . Leakage effects should not be considered in this question.

a. Assume that the initial voltage on  $V_{out} = 0$ . A step from 0 to  $V_{DD}$  is applied at the input. Determine the final voltage at  $V_{out}$ .

$$V_{OUT} = V_{Z} = V_{I} = V_{GS} - V_{T} = V_{DD} - V_{I}$$

$$V_{T} = V_{Tn} + 8 \left[ \sqrt{-2\phi_{F} + V_{SB}} - \sqrt{-2\phi_{F}} \right]; V_{SB} = V_{I}$$

body effect

$$2.5 - V_{1} = 0.4 + 0.4 \left[ \int_{0.6+V_{1}}^{0.6+V_{1}} - \int_{0.6}^{0.6} \right]$$

$$(2.41 - V_{1})^{2} = (0.4 \int_{0.6+V_{1}}^{0.6+V_{1}})^{2}$$

$$2.41^{2} - 4.82V_{1} + V_{1} = (0.16)(0.6+V_{1})$$

$$V_{1}^{2} - 4.916V_{1} + 5.664 = 0$$

$$(trial = error) as well$$

$$V_{out}$$

(final) = 1.843  $\vee$

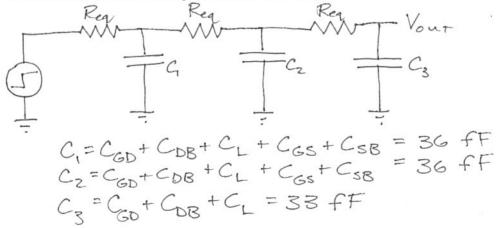

b. Assume the following parameters for the minimum size transistors:  $R_{eq} = 15 \text{ k}\Omega$ ,  $C_{gs} =$  $C_{gd} = C_{gb} = 1$  fF.  $C_{sb} = C_{db} = 2$  fF. To determine the propagation delay of the circuit, we will use the equivalent resistor-capacitor diagram. Draw the equivalent circuit including all relevant resistors and capacitors and their values.

c. Determine the **propagation delay** between input and output for a step at the input from 0 to Vdd.

(1.5)

$$T = R_{eq}C_1 + 2R_{eq}C_2 + 3R_{eq}C_3$$

$= (15k)(36f) + (30k)(36f) + (45k)(33f)$

$= 3.105 \text{ ns}$

(6.5)  $t_{pd} = 0.69 T = 2.142 \text{ ns}$

$$t_{p(\text{for Vin going from }\theta \to \text{Vdd})} = 2.142 \text{ nS}$$

d. Assuming that the transistor capacitors and conductance increase linearly with the width of the transistor. Determine the size S of the transistors that reduces the propagation delay by a factor of 2. All three transistors are to be scaled by the same factor..

$$\frac{T_{S}}{S} = \frac{R_{eq}}{S} \left( 6f \cdot S + C_{L} \right) + \frac{2R_{eq}}{S} \left( 6f \cdot S + C_{L} \right) + \frac{3R_{eq}}{S} \left( 3f \cdot S + C_{L} \right) \\

= \frac{T_{S}}{S} = \frac{T_{S}}{S} \\

= \frac{1}{2} \left[ 36 + 72 + 99 \right] = \left( \frac{1}{5} \right) \left[ 6S + 30 + 12S + 60 + 9S + 90 \right] \\

= 76.55 \cdot S = 180 \\

= 2.353$$

$$S = (W/L) / (W/L)_{orig} = 2.353$$

## Problem 2: Device Analysis

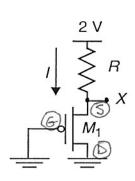

Consider the device configuration of FIG. 2. M1 is a minimum size transistor (assume W/L = 1). Assume the transistor parameters given on page 1 of the midterm, but assume that  $\gamma = 0$  (no bodyeffect). Assume a short-channel transistor modeled by the unified model ..

a. Write down the equations (and only those) that you need to determine the voltage at node X. Do NOT plug in any values yet. BE COMPLETE and CONSIDER ALL POSSIBLE SOLUTIONS. FIG. 2 CMOS inverter with resistive load

Determine for each solution when it is valid.

Notice that

$$V_{GS} = V_{DS}$$

.:  $M_1$  is always either in saturation or vel. saturation

$$I_D = \frac{2 - V_X}{R}$$

If  $M_1$  in saturation  $(V_X < IV)$ ,  $V_{MIN} = |V_{GS}| - |V_T| = 0.8 \cdot 0.4$

$$I_D = \frac{1}{2} k_p \left(\frac{\omega}{L}\right) \left[ \left(|V_X| - |V_{TP}|\right)^2 \right]$$

If M, in vel. saturation

$$\begin{bmatrix}

I_{D} = Z R_{P} \left( L \right) \left[ \left( |V_{X}| - |V_{T_{P}}| \right) \right] \\

I_{D} = k_{P} \left( \frac{\omega}{L} \right) \left[ \left( |V_{X}| - |V_{T_{P}}| \right) |V_{DSAT_{P}}| - \frac{|V_{DSAT_{P}}|^{2}}{Z} \right]$$

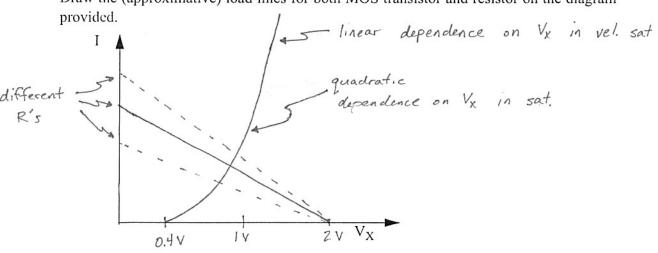

b. We would like to place  $V_X$  at 0.8 V. Determine which of the above soltuions is valid. Draw the (approximative) load lines for both MOS transistor and resistor on the diagram

c. Determine the value of the resistance required to place X at 0.8V.

If

$$V_x = 0.8V$$

, M, in saturation since  $|V_{0S}| < |V_{0SATp}|$

$$\frac{2-0.8}{R} = (\frac{1}{2})(30.10^{-6})(0.8-0.4)^2$$

$$R = \frac{1.2}{2.4} \frac{V}{\mu A} = 500 \, k\Omega$$

d. Assume now that the  $\lambda$ -factor of the PMOS is different from 0, in contrast to what was assumed so far. Determine qualitatively if the voltage at node X will go down, or up, or remain unchanged. Explain your answer.

| Up Down   | if | Ap \$0, then more current | I increases, drawing through R |

|-----------|----|---------------------------|--------------------------------|

| Unchanged |    |                           | across R is larger             |

|           |    | -> therefore              | Vx must decrease               |

## PROBLEM 3: Technology Scaling

Consider a CMOS inverter followed by a wire on length L. Assume that in the reference design, inverter and wire contribute equally to the total propagation delay  $t_{pref}$ . You may assume that the transistors are velocity-saturated. The wire is scaled in line with the **ideal** wire scaling model. Assume initially that the wire is a local wire.

a. Determine the new (total) propagation delay as a a function of  $t_{pref}$ , assuming that technology and supply voltage scale with a factor 2. Consider only first-order effects.

Delay of buffer scales as &

Delay of local wires scales as 1

$$t_p = \frac{t_p \, buffer}{2} + t_p wire = \frac{t_p ref}{4} + \frac{t_p ref}{2} = \frac{3}{4} t_p ref$$

$$t_p = 3/4 t_{pref}$$

b. Perform the same analysis, assuming now that the wire scales a **global wire**, and the wire length scales inversely proportional to the technology.

c. Repeat b, but assume now that the wire is scaled along the constant resistance model. You may ignore the effect of the fringing capacitance.

may ignore the effect of the fringing capacitance.

Delay of global wire (constant resistance) scales as

$$5^3$$

$t_0 = \frac{t_{pref}}{4} + \frac{t_{pref}}{2} \cdot 8 = \frac{17}{4} t_{pref}$

$$D t_p = 17/4 t_{pref}$$

d. Repeat b, but assume that the new technology uses a better wiring material that reduces the resistivity by half, and a dielectric with a 25% smaller permittivity.

$$t_p = \frac{13}{4} t_{pref}$$

0

0.5

0.5

e. Discuss the energy dissipation of a. as a function of the energy dissipation of the original design  $E_{ref}$ .

$$E_{buffer} \sim CV^2$$

$E_{wire} \sim CV^2$

$V \rightarrow V_S$

So

Ebuffer scales as

$$\frac{1}{5^3}$$

Ewire scales as  $\frac{1}{5^3}$

$E = \frac{\text{Eref}}{2} \cdot (\frac{1}{8}) + \frac{\text{Eref}}{2} \cdot \frac{1}{8}$

$E = \frac{1}{8} \text{ Eref}$

f. Determine for each of the statements below if it is true, false, or undefined, and explain in one line your answer.

- When driving a small fan-out, increasing the driver transistor sizes raises the short-circuit power dissipation (T) F-U Overdriving the output causes the output fall time to be much smaller than the input rise time, increasing s.c. power

- Reducing the supply voltage, while keeping the threshold voltage constant decreases the short-circuit power dissipation (T) F U Less time when both transistors are on

- o.s Moving to Copper wires on a chip will enable us to build faster adders. T (F) U

RC delay is not an issue for short wires

- RC delay is not an issue for short wires

Making a wire wider helps to reduce its RC delay. T-F (U)

- Only when fringing is an issue, but making a wide wire wider

Going to dielectrics with a lower permittivity will make RC wire delay more important.

T-F-U

RC scales down in the same way as C -> impact remains the same.