# University of California College of Engineering Department of Electrical Engineering and Computer Sciences

E. Alon

Saturday, December 13, 2008 12:30-3:30pm

# EECS 141: FALL 2008—FINAL EXAM

For all problems, you can assume that all transistors have a channel length of 100nm and the following parameters (unless otherwise mentioned):

| NMOS:                                                                         |                              |                                  |                                 |

|-------------------------------------------------------------------------------|------------------------------|----------------------------------|---------------------------------|

| $V_{Tn} = 0.2 \text{V}, \ \mu_n = 400 \text{ cm}^2/(\text{V} \cdot \text{s})$ | $C_{ox} = 1.125  \mu F/cm^2$ | $v_{sat} = 1e7 \text{ cm/s}, L=$ | =100nm, $\gamma$ = $\lambda$ =0 |

**PMOS:**  $|V_{Tp}| = 0.2 \text{V}, \ \mu_p = 200 \text{ cm}^2/(\text{V} \cdot \text{s}), \ C_{ox} = 1.125 \ \mu\text{F/cm}^2, \ v_{sat} = 1e7 \text{ cm/s}, \ L=100 \text{nm}, \ \gamma = \lambda = 0$

| NAME     | Last    | First |  |

|----------|---------|-------|--|

| GRAD/UNI | DERGRAD |       |  |

| Problem | 1: | / | 16 |

|---------|----|---|----|

|---------|----|---|----|

# PROBLEM 1: Logic Styles and LE (16 pts)

For this problem, you can assume that  $C_G=C_D=2fF/\mu m,\ R_{sqn}=10k\Omega/\Box,\ R_{sqp}=20k\Omega/\Box,$  and that the transistors are quadratic (i.e., long-channel).

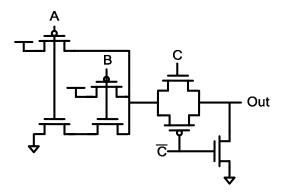

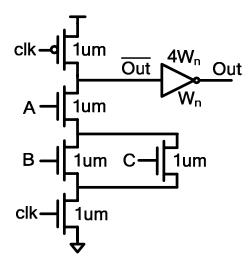

a) (3 pts) What logical function does the gate shown below implement?

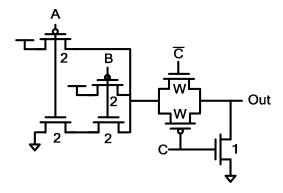

**b)** (7 **pts**) Given the sizing shown below, what value of W would you use in order to make the worst-case LE of the C input equal to half the LE of the A and B inputs (i.e.,  $LE_C = \frac{1}{2}LE_A$ )? What would be the LE of the C input in this case?

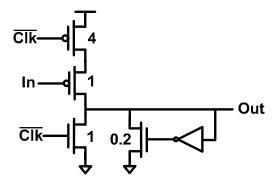

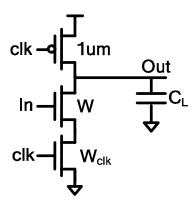

c) (6 pts) During evaluation, what is the logical effort of the dynamic gate shown below from input In?

#### **PROBLEM 2: SRAM Design (14 points)**

For this problem you should use the velocity saturated transistor model.

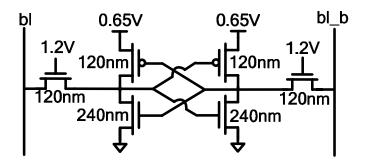

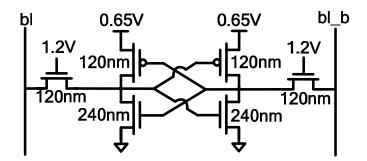

a) (8 pts) Shown below is an SRAM cell during a read, where the power supply of the SRAM has been reduced to 0.65V while the  $V_{DD}$  of the wordline is 1.2V. Note that the bitlines have also been precharged to 0.65V. With the device sizing shown below, what is the read  $\Delta V$ ? (Hint: How much larger is  $I_{DSAT}$  for a transistor with  $V_{GS} = 1.2V$  than with  $V_{GS} = 0.65V$ ?)

**b)** (**6 pts**) Assuming that in your answer to part a) you calculated that the pull-down device is saturated, how much faster does the SRAM cell pull down the bitline when the wordline is driven to 1.2V compared to if the wordline was driven to only 0.65V? (Note that most of the credit on this problem will be given for finding the right regions of operation and setting up the equations.)

### PROBLEM 3: Dynamic Logic Design (24 pts)

For this problem, you can assume that  $V_{DD}$  = 1.2V,  $C_G$  = 2fF/ $\mu$ m, and  $C_D$  = 1fF/ $\mu$ m.

a) (6 pts) In the domino gate shown below, what is the minimum  $W_n$  necessary to ensure that the gate does not fail due to charge sharing? You can assume that with the sizing shown, the  $V_{IH}$  of the inverter is  $\sqrt[3]{4} \cdot V_{DD}$ , and that none of the source/drain regions have been shared.

**b)** (6 pts) Other than changing W<sub>n</sub>, the sizes of the transistors in the dynamic gate, or adding a keeper, what else can change in the gate from part a) in order to mitigate the charge sharing issue? You should explain your changes and draw a new transistor-level schematic of the gate (no sizing necessary). To receive full credit on this problem, you should identify two independent changes; if you identify three changes you will receive bonus credit.

c) (2 pts) On the evaluation edge, what is the delay of the dynamic gate shown below as a function of  $R_{sq,n}$ ,  $C_L$ , W, and  $W_{clk}$ ? You can assume that  $C_D = 0$  and ignore slope effect.

d) (2 pts) Assuming that In has an activity factor of  $\alpha_{0 \to 1}$ , how much power is consumed due to driving In? How about due to driving clk? You should provide your answers in terms of W,  $W_{clk}$ ,  $\alpha_{0 \to 1}$ ,  $C_G$ ,  $V_{DD}$ , and f.

| e) | (8 pts) Increasing the size of the evaluation transistor (i.e., increasing $W_{clk}$ ) speeds up the dynamic inverter, but costs power. Using the results from parts c) and d), can you find an optimal $W_{clk}/W$ ? |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                                       |

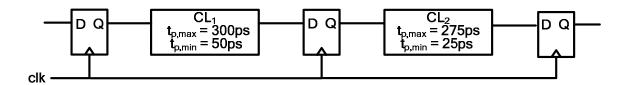

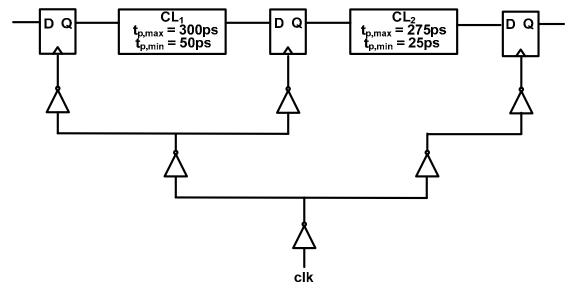

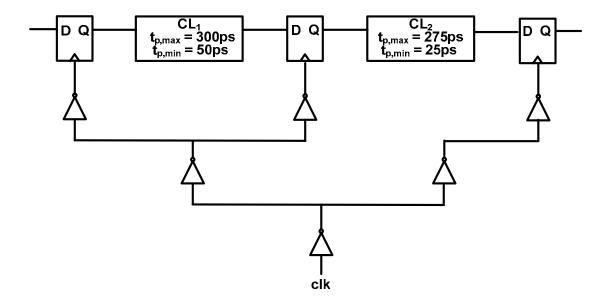

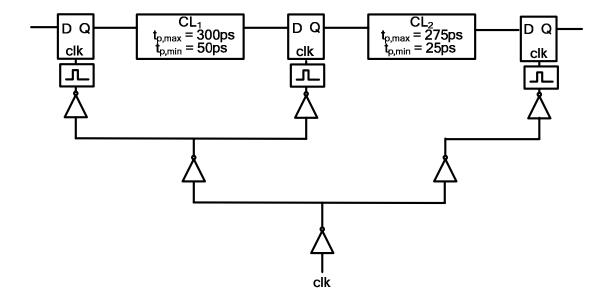

# **PROBLEM 4: Timing and Clock Distribution (24 points)**

In this problem we will be examining the pipeline shown below. The minimum and maximum delays through the logic are annotated on the figure, and the flip-flops have the following properties:  $t_{clk-q} = 50$ ps,  $t_{setup} = 25$ ps, and  $t_{hold} = 25$ ps. You can assume that the clock has no jitter.

**a) (6 pts)** What is the minimum clock cycle time for this pipeline? Are there any minimum delay violations?

**b)** (**4 pts**) Now we'll include the clock distribution network for this pipeline. Assuming that the delay of each inverter is nominally 50ps, but that each inverter's delay varies randomly by +/-20%, now what is the minimum clock cycle time?

c) (4 pts) Under these same conditions (i.e., 50ps nominal inverter delay, +/-20% delay variation), can this pipeline fail any minimum delay constraints?

**d)** (10 pts) If we replace the flip flops by pulsed latches with the same  $t_{clk-q}$ ,  $t_{setup}$ , and  $t_{hold}$  as the flip-flops, and with  $t_{d-q} = t_{clk-q} + t_{setup}$ , can the minimum cycle time of the pipeline be reduced without potentially failing a minimum delay constraint? If so, how wide must the pulses be, and what is the new minimum cycle time? If not, explain which path fails the minimum delay constraint.

# PROBLEM 5: Arithmetic (18 pts)

In this problem we will look at designing a comparator whose output  $C_{out} = 1$  whenever A > B, where A and B are unsigned binary numbers. Throughout this problem you can assume that you have both the true and complement versions of the inputs available to you.

a) (2 pts) If A and B are both only a single bit, draw a gate-level schematic (i.e., no transistors) showing how you would compute  $C_{out}$ .

**b)** (5 pts) Now assume that A and B are both two bit numbers -i.e., we have inputs  $A_{1:0}$  and  $B_{1:0}$ . To compare between  $A_0$  and  $B_0$  we can use the "half comparator" circuit you drew in part a). Draw a gate level schematic showing how you would implement a "full comparator" and use it to calculate the final  $C_{out}$ .

| c) | (5 pts) Notice that these comparators have several characteristics that are very                |

|----|-------------------------------------------------------------------------------------------------|

|    | similar to adders. As a function of A and B, define new P (propagate) and G                     |

|    | (generate) signals that are appropriate for comparators, and then write the logic               |

|    | equation that gives the C <sub>out</sub> for a particular bit using P, G, and C <sub>in</sub> . |

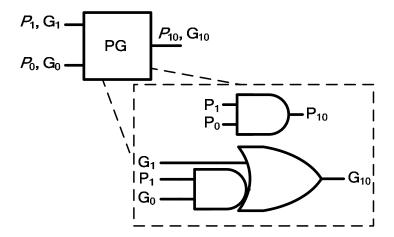

**d)** (**6 pts**) Given your definitions from part c), sketch a block diagram showing how you can implement an 8-bit "carry lookahead" comparator using the PG block shown below.

EECS 141: FALL 2008 - FINAL EXAM