# University of California College of Engineering Department of Electrical Engineering and Computer Science

J. M. Rabaey B. Nikolic TuTh9:30-11am ee141@eecs

# EECS 141: FALL 99 —MIDTERM 2

For all problems, you can assume the following transistor parameters (unless otherwise mentioned):

**NMOS:**

$$V_{Tn} = 0.4$$

,  $k'_n = 115 \mu A/V^2$ ,  $V_{DSAT} = 0.6V$ ,  $\lambda = 0$ ,  $\gamma = 0.4 V^{1/2}$ ,  $2\Phi_F = -0.6V$

**PMOS:**

$$V_{Tp} = \text{-0.4V, k'}_p = \text{-30 } \mu\text{A/V}^2, \, V_{DSAT} = \text{-1V, } \lambda = 0, \, \gamma = \text{-0.4 } V^{1/2}, \, 2\Phi_F = 0.6 V$$

|        |      |      |       |       |     | <br> |  |

|--------|------|------|-------|-------|-----|------|--|

|        |      |      |       |       |     |      |  |

|        |      |      |       |       |     |      |  |

| NAME   |      |      |       |       |     |      |  |

| NAIVIE |      | 0    |       |       |     |      |  |

|        | Last | SOLU | TIONS | Firs  | t t |      |  |

|        | Lasi | -    | • • • | 1 110 |     |      |  |

GRAD/UNDERGRAD

Problem 1: 5

Problem 2: 4

Problem 3: 4

Problem 4: 7

Total 20

GOOD LUCK!!

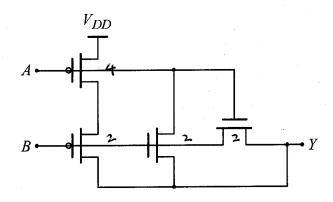

### 1. Pass-transistor Logic

A pass-transistor network is shown in FIG. 1. Assume that inputs A and B are ideal voltage sources.  $V_{DD}=2.5\mathrm{V}$ . The gate capacitances are constant and equal to 4fF, and all drain/source capacitances are equal to 2fF (all these capacitances can be considered as capacitances to ground). The load capacitor connected to the output is  $C_L=10$  fF. The equivalent resistance of an NMOS transistor with W/L=1 is  $15\mathrm{k}\Omega$ , while the equivalent resistance of a PMOS with W/L = 1 equals  $50\mathrm{k}\Omega$ . The NMOS transistors have W/L=2 and PMOS transistors have W/L=4.

FIG. 1 Pass-transistor network

a. For all the possible combinations of inputs A and B find the output voltage levels.

| A        | В        | Y                 |

|----------|----------|-------------------|

| 0        | 0        | V00 = 2.5 V       |

| 0        | $V_{DD}$ | ø                 |

| $V_{DD}$ | 0        | Ø                 |

| $V_{DD}$ | $V_{DD}$ | V00 - VT = 1.86 V |

$$V_{T} = V_{T0} + \delta(\sqrt{1-20} + V_{SB}) - \sqrt{pop})$$

$$= 0.4 + 0.4 \left[\sqrt{2.5 - 0.6} - \sqrt{0.6}\right]$$

$$= 0.64V$$

b) What logic function Y = f(A, B) is implemented by this network?

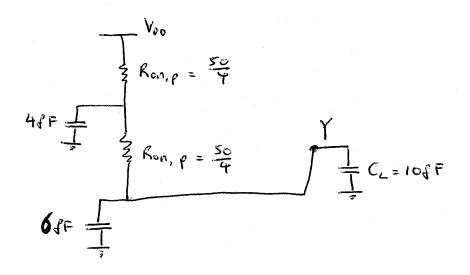

c) Find the propagation delay (from  $V_{DD}/2$  to  $V_{DD}/2$ ) of this network when B=0, and A switches instantaneously from  $V_{DD}$  to 0.

From Vog/2 to Vog/2 simply means the propagation delay as we have defined in class from 2nd week.

$$T = 4f(\frac{50k}{4}) + 16f(\frac{100k}{4}) = 450 ps$$

$t_p = 0.69 T = 310 ps$

#### 2. Miscellaneous Problems

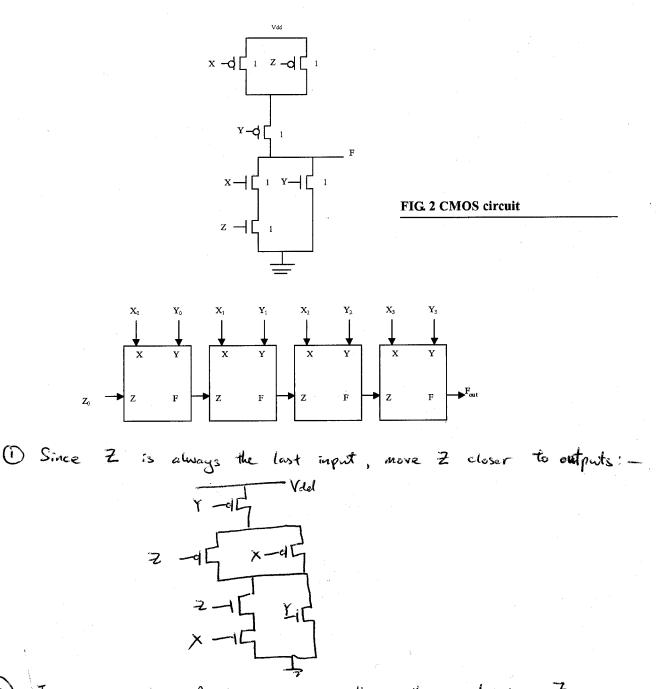

a. The complementary CMOS circuit shown in the Figure is used in the more complex network shown below. Indicate **2 ways** on how you would modify the CMOS circuit such that the delay between  $Z_0$  and  $F_{out}$  is minimized (you are to stick to static complementary static CMOS). Redraw the circuit if needed.

2 Increase paths of transistors in the paths containing Z. \( \frac{1}{2} \) 3 Progressively sizing X input in PDN; Y input in PUN. b. What is the potential problem with the circuit shown below? Add or change ONE transistor to remedy the problem.

#### **Problem:**

Level restoring PMOS does not help charge sharing for the PUN. We need to add an NMOS to drain the potential charge.

Other Partial Credit's Problems

1: Increased delay due to fighting NMOS/PMOS

1: Charge Sharing

Other Solutions:

1: Stat: NMOS bleeder

# 3. Power dissipation

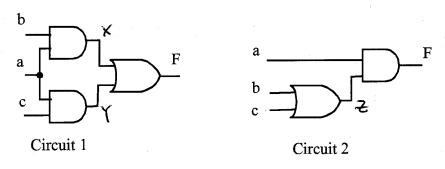

The two circuits shown in FIG. 3 (obviously) perform the same logic function. Assume that the gates are implemented (somehow) using complimentary CMOS logic, and that all the nodes in the network have the same capacitance C. The input signals have the following probabilities of being "1":  $P_a = 0.1$ ,  $P_b = 0.5$ , and  $P_c = 0.5$ . Determine which implementation consumes the least power and why. Be precise.

#### FIG. 3 Logic Circuits

1.5

1-5

Both circuits have equivalent logic

$$\Rightarrow \text{ Switching probabilities Q F are the same}$$

$$\therefore \text{ Consider only input nodes}.$$

$$P(X=1) = Pa P_b = 0.05$$

$$P(Y=1) = Pa P_c = 0.05$$

$$P_{o-3}(X) = P_{o-3}(Y)$$

$$= 0.05(1-0.05)$$

$$= 0.0475$$

$$P(Z=0) = (1-P_b)(1-P_c) = \frac{1}{4}$$

$$P_{o-3}(Z) = \frac{3}{4}, \frac{1}{4} = \frac{3}{16}$$

Circuit with lowest power dissipation:

Why: Combined power of internal nodes:

$$Ckt 1: CV_{dd}^{2} f(2 \times 0.0475)$$

$$Ckt 2: CV_{dd}^{2} f(\frac{3}{6})$$

$$Ckt 1 has less power consumption$$

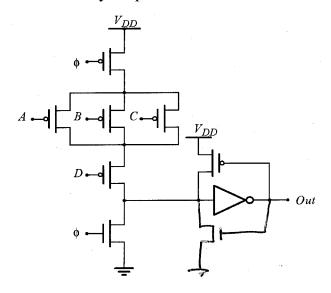

## 4. Wiring

2

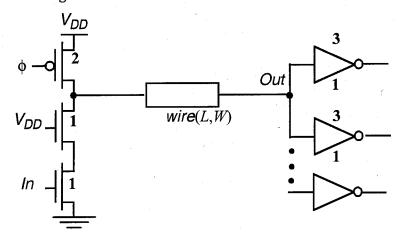

FIG. 4 Digital circuit. The numbers annotated indicate the  $W\!/\!L$  ratios of the transistors

A dynamic 2-input NAND gate drives a wire of length L and width W, connecting to a fanout of F identical static CMOS inverters (Figure 1). Assume the following parameters:

NMOS transistor (per unit width):  $R_n$ ;  $C_{gn} = 2C_t$ ;  $C_{dn} = C_{sn} = C_t$

PMOS transistor (per unit width):  $R_p = 3R_n$ ;  $C_{gp} = 2C_t$ ;  $C_{dp} = C_{sp} = C_t$ ;

(these are the only transistor capacitors you should consider, and all of them are from terminal to ground)

Wire parameters:  $r_{sq}$  (sheet resistance);  $c_a$  (area capacitance per unit area);  $c_f$  (fringe capacitance per unit length)

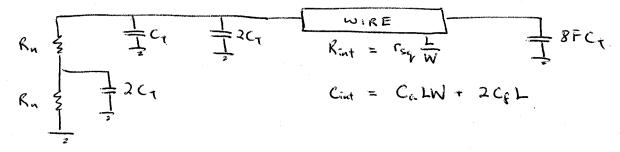

a. Draw the equivalent circuit diagram that you plan to use to determine the propagation delay of the circuit for a 0 -> 1 transition on In (assuming  $\phi$  is high). Indicate all important elements (capacitances and resistances) and provide expressions for their values.

b. Derive a symbolic expression for the propagation delay of the network between *In* and *Out* for a 0-to-1 transition at *In*.

Using Elmore's Delay model

$$tp = 0.69 \begin{cases} Rn(2C_t) + 2Rn(C_t + 2C_t) + 2Rn(C_{int}) \\ + (2Rn + R_{int})(8FC_t) \end{cases} + \text{Wire Delay}$$

$$= 0.69 \left(4RnC_t + 2RnC_t + 2RnC_{int} + 16RnFC_t + 8R_{int}FC_t\right) + 0.38R_{int}C_{int}$$

c. Assume that all transistors in the NMOS pull-down network have the same width.

Determine the absolute minimum value of the propagation delay that can be obtained by the sizing of the transistors in the pull-down network of the NAND gate.

Can size width of NMOS infinitely large

$$R_n \rightarrow 0$$

but  $R_n C_{\uparrow}$  remains constant for NMOS.

Note that one of the  $2R_n C_{\uparrow}$  terms above is contributed by PMOS transistor, which does not scale  $\Rightarrow 2R_n C_{\uparrow} \rightarrow 0$

d. Alternatively, assume that we would try to reduce the propagation delay by increasing the wire width. Determine the absolute minimum propagation delay that can be obtained that way.

All the terms in answer to part (b) remain constant except

As we increase width of wire, area capacitance will dominate over fringe cap.

What remains is the term

Min. when the 2 terms are equal: -

$$2R_{n}C_{a}WL = 8F r_{eq} \frac{L}{W}C_{t}$$

$$W = \sqrt{\frac{8F r_{eq} L C_{t}}{2R_{n}C_{ci} L}}$$

Min. delay occurs when W set as above.